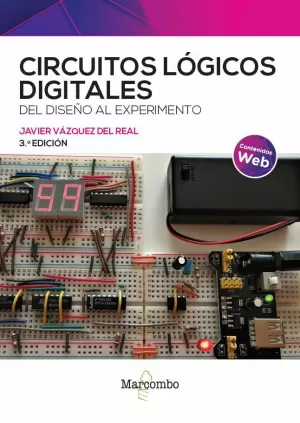

- Editorial:

- MARCOMBO

- Año de edición:

- 2023

- ISBN:

- 978-84-267-3595-9

- Páginas:

- 758

CIRCUITOS LÓGICOS DIGITALES 3ED

VÁZQUEZ DEL REAL, JAVIER

Presentación ...................................................................................................... xxiii

PARTE 1 Familias lógicas ........................................................................ 1

1 Puertas lógicas TTL ........................................................................................... 3

1.1 Introducción ............................................................................................................... 3

1.2 Estructura de una puerta TTL NAND de dos entradas .............................................. 4

1.3 Cargabilidad de salida de una puerta inversora TTL ................................................. 7

1.3.1 Estimación analítica .......................................................................................... 7

1.3.2 Análisis mediante PSpice ................................................................................. 9

1.4 Características de transferencia .............................................................................. 13

1.4.1 Puerta inversora TTL estándar ....................................................................... 13

1.4.2 Puerta inversora (CI 7404) ............................................................................. 16

1.4.3 Puerta NAND (CI 7400) .................................................................................. 17

1.5 Entradas flotantes en puertas TTL .......................................................................... 19

1.5.1 El riesgo potencial de las entradas flotantes ................................................. 19

1.5.2 ¿Qué hacer con las entradas no utilizadas? ................................................... 20

1.6 Caracterización temporal ........................................................................................ 21

1.6.1 Parámetros característicos ............................................................................. 21

1.6.2 Oscilador en anillo .......................................................................................... 25

1.7 Componentes .......................................................................................................... 27

1.8 Verificación experimental ........................................................................................ 27

1.8.1 Obtención de las tablas de verdad ................................................................. 27

1.8.1.1 Función lógica NOT (inversión) .............................................................. 28

1.8.1.2 Función lógica NAND ............................................................................. 28

1.8.1.3 Función lógica NOR ............................................................................... 29

1.8.2 Cargabilidad de salida .................................................................................... 30

1.8.2.1 Estimación de la resistencia de salida de un dispositivo ....................... 30

1.8.3 Características de transferencia de un inversor .............................................. 31

1.8.3.1 Característica de transferencia vs(ve) ..................................................... 31

1.8.3.2 Característica de transferencia ie(ve) ...................................................... 32

1.8.4 Entradas flotantes en una puerta NAND (CI 74x00) ....................................... 33

1.8.5 Caracterización temporal: oscilador en anillo ................................................. 33

1.9 Ejercicios y cuestiones de refuerzo ......................................................................... 34

2 Puertas lógicas CMOS ..................................................................................... 35

2.1 Introducción ............................................................................................................. 35

2.2 Estructura de una puerta CMOS NAND de dos entradas ........................................ 38

2.3 Cargabilidad de salida de una puerta CMOS NAND .................................................... 39

2.3.1 Consideraciones preliminares ......................................................................... 39

2.3.2 Análisis mediante PSpice ................................................................................ 42

2.3.2.1 Caso de estudio 1 ................................................................................... 44

2.3.2.2 Caso de estudio 2 ................................................................................... 46

2.3.2.3 Caso de estudio 3 ................................................................................... 48

2.3.2.4 Cargabilidad del CI 4011B ...................................................................... 50

2.4 Características de transferencia .............................................................................. 51

2.5 Entradas flotantes en puertas CMOS ...................................................................... 57

2.6 Componentes .......................................................................................................... 58

2.7 Verificación experimental ......................................................................................... 58

2.7.1 Cargabilidad de salida ..................................................................................... 58

2.7.2 Características de transferencia de un inversor CMOS .................................. 59

2.7.2.1 Característica de transferencia vs(ve) ..................................................... 60

2.7.2.2 Característica de transferencia ie(ve) ...................................................... 60

2.7.3 Entradas flotantes en una puerta NAND (CI 4011B) ....................................... 61

2.8 Ejercicios y cuestiones de refuerzo ......................................................................... 62

PARTE 2 Lógica combinacional ............................................................ 65

3 Decodificador binario básico de 2 a 4 ............................................................ 67

3.1 Introducción ............................................................................................................. 65

3.2 Decodificador binario básico de 2 a 4 ...................................................................... 71

3.2.1 Decodificación con salidas activas a nivel alto ................................................ 71

3.2.2 Decodificación con salidas activas a nivel bajo ............................................... 72

3.3 Simulación ............................................................................................................... 75

3.3.1 Decodificación con salidas activas a nivel alto ................................................ 75

3.3.2 Decodificación con salidas activas a nivel bajo ............................................... 76

3.4 Componentes .......................................................................................................... 77

3.5 Verificación experimental ......................................................................................... 78

3.5.1 Decodificación con salidas activas a nivel alto ................................................ 78

3.5.2 Decodificación con salidas activas a nivel bajo ............................................... 79

3.6 Ejercicios y cuestiones de refuerzo ......................................................................... 79

4 Síntesis óptima de circuitos combinacionales ............................................. 81

4.1 Introducción ............................................................................................................. 81

4.2 Síntesis en forma de suma de productos (AND-OR) ............................................... 83

4.3 Síntesis en forma de producto de sumas (OR-AND) ............................................... 86

4.4 Síntesis de dos niveles NAND-NAND ...................................................................... 89

4.5 Síntesis de dos niveles NOR-NOR .......................................................................... 90

4.6 Síntesis multinivel con puertas NAND de dos entradas ........................................... 90

4.7 Análisis transitorio: fenómenos aleatorios ................................................................ 94

4.7.1 Tipos de fenómenos aleatorios ....................................................................... 95

4.7.2 Fenómenos aleatorios de función ................................................................... 96

4.7.3 Eliminación de fenómenos aleatorios .............................................................. 99

4.8 Simulación ............................................................................................................. 100

4.8.2 Análisis transitorio ......................................................................................... 101

4.9 Componentes ........................................................................................................ 106

4.10 Verificación experimental .................................................................................... 106

4.11 Ejercicios y cuestiones de refuerzo ..................................................................... 108

5 Codificador binario básico de 4 a 2 .............................................................. 109

5.1 Introducción ........................................................................................................... 109

5.2 Codificador binario básico de 4 a 2 sin prioridad ................................................... 111

5.2.1 Codificación con entradas activas a nivel alto .............................................. 111

5.2.2 Codificación con entradas activas a nivel bajo ............................................. 112

5.3 Codificador binario básico de 4 a 2 con prioridad .................................................. 113

5.3.1 Codificación con entradas activas a nivel alto .............................................. 113

5.3.2 Codificación con entradas activas a nivel bajo ............................................. 116

5.4 Simulación ............................................................................................................. 117

5.4.1 Circuitos codificadores de 4 a 2 sin prioridad ............................................... 118

5.4.1.1 Codificación con entradas activas a nivel alto ...................................... 118

5.4.1.2 Codificación con entradas activas a nivel bajo ..................................... 118

5.4.2 Circuitos codificadores de 4 a 2 con prioridad .............................................. 119

5.4.2.1 Codificación con entradas activas a nivel alto ...................................... 119

5.4.2.2 Codificación con entradas activas a nivel bajo ..................................... 120

5.5 Componentes ........................................................................................................ 121

5.6 Verificación experimental ...................................................................................... 122

5.6.1 Codificación sin prioridad y entradas activas a nivel bajo ............................. 122

5.6.2 Codificación con prioridad y entradas activas a nivel bajo ............................ 122

5.7 Ejercicios y cuestiones de refuerzo ....................................................................... 123

6 Circuitos comparadores, de paridad y conversores de código ................ 125

6.1 Introducción ........................................................................................................... 125

6.2 Circuitos aritméticos comparadores ...................................................................... 127

6.3 Circuito generador y circuito detector de paridad .................................................. 129

6.4 Circuitos conversores de código ........................................................................... 131

6.5 Simulación ............................................................................................................. 135

6.5.1 Circuito comparador ..................................................................................... 135

6.5.2 Circuito generador de paridad ...................................................................... 136

6.5.3 Circuitos conversores de código ................................................................... 137

6.6 Componentes ........................................................................................................ 139

6.7 Verificación experimental ...................................................................................... 139

6.7.1 Circuito comparador ..................................................................................... 139

6.7.2 Circuito generador de paridad ...................................................................... 139

6.7.3 Circuitos conversores de código ................................................................... 140

6.8 Ejercicios y cuestiones de refuerzo ....................................................................... 140

7 Decodificador binario de 2 a 4 con control de polaridad ........................... 143

7.1 Introducción ........................................................................................................... 143

7.2 Decodificador binario básico de 2 a 4 con control de polaridad ............................ 144

7.2.1 Tres síntesis distintas con puertas NAND de dos entradas .......................... 145

7.2.2 Síntesis con puertas NAND de cualquier número de entradas ..................... 147

7.2.3 Síntesis basada en puertas XOR .................................................................. 150

7.3 Simulación ............................................................................................................. 151

7.4 Componentes ........................................................................................................ 152

7.5 Verificación experimental ....................................................................................... 153

7.6 Ejercicios y cuestiones de refuerzo ....................................................................... 153

8 Detección de números primos con multiplexores .................................... 155

8.1 Introducción ........................................................................................................... 155

8.2 Diseño de un detector BCD de números primos .................................................... 158

8.2.1 Síntesis mediante puertas lógicas ................................................................. 158

8.2.2 Síntesis mediante un multiplexor 16:1........................................................... 159

8.2.3 Síntesis mediante un multiplexor 8:1............................................................. 160

8.2.4 Síntesis alternativa mediante un multiplexor 8:1 ........................................... 161

8.3 Diseño de un detector de números primos de 4 bits .............................................. 163

8.3.1 Síntesis mediante puertas lógicas ................................................................. 163

8.3.2 Síntesis mediante un multiplexor 16:1........................................................... 164

8.3.3 Síntesis mediante dos multiplexores 8:1 ....................................................... 165

8.3.4 Síntesis alternativa mediante un multiplexor 8:1 ........................................... 166

8.4 Simulación ............................................................................................................. 167

8.4.1 Detectores BCD de números primos con multiplexor .................................... 167

8.4.1.1 Síntesis mediante un multiplexor 16:1 .................................................. 167

8.4.1.2 Síntesis mediante un multiplexor 8:1 .................................................... 168

8.4.1.3 Síntesis alternativa mediante un multiplexor 8:1 .................................. 169

8.4.2 Detectores de números primos de 4 bits con multiplexor .............................. 169

8.4.2.1 Síntesis mediante un multiplexor 16:1 .................................................. 169

8.4.2.2 Síntesis mediante dos multiplexores 8:1 .............................................. 170

8.4.2.3 Síntesis alternativa mediante un multiplexor 8:1 .................................. 171

8.5 Componentes ........................................................................................................ 172

8.6 Verificación experimental ....................................................................................... 172

8.7 Ejercicios y cuestiones de refuerzo ....................................................................... 173

9 Sumador completo y sumador binario en paralelo ..................................... 175

9.1 Introducción ........................................................................................................... 175

9.2 Circuito semisumador ............................................................................................ 176

9.3 Circuito sumador completo .................................................................................... 177

9.4 Implementaciones de un sumador completo ......................................................... 179

9.4.1 Síntesis de dos niveles AND-OR mediante PAL ........................................... 179

9.4.2 Síntesis de dos niveles NAND-NAND ........................................................... 180

9.4.3 Dos síntesis de seis niveles con puertas básicas ......................................... 182

9.4.4 Síntesis de cuatro niveles con puertas NAND de tres entradas .................... 184

9.4.5 Síntesis de dos niveles basada en puertas XOR y NAND ............................ 184

9.4.6 Síntesis de tres niveles basada en puertas XOR y NAND ............................ 185

9.5 Sumador binario en paralelo con acarreo serie ..................................................... 187

9.6 Simulación ............................................................................................................. 189

9.6.1 Semisumador ............................................................................................... 189

9.6.2 Sumador completo ........................................................................................ 190

9.6.3 Sumador binario de 4 bits con acarreo en serie ............................................ 191

9.6.3.1 Propagación del acarreo y retardo asociado ........................................ 191

9.7 Componentes ........................................................................................................ 193

9.8 Verificación experimental ...................................................................................... 193

9.8.1 Semisumador ................................................................................................ 193

9.8.2 Sumador completo ........................................................................................ 194

9.8.3 Sumador binario de 2 bits con acarreo en serie ........................................... 194

9.9 Ejercicios y cuestiones de refuerzo ....................................................................... 195

10 Unidad aritmética de 4 bits en complemento a dos ................................ 197

10.1 Introducción ......................................................................................................... 197

10.2 Diseño de una unidad aritmética de 4 bits en C2 ................................................. 198

10.2.1 El sumador 74x283 ..................................................................................... 198

10.2.2 La puerta XOR como solución para implementar la resta .......................... 199

10.2.3 El detector de desbordamiento ................................................................... 201

10.2.4 Unidad aritmética completa ........................................................................ 202

10.3 Simulación ........................................................................................................... 203

10.3.1 Módulo sumador ......................................................................................... 203

10.3.2 Módulo sumador/restador ........................................................................... 205

10.3.3 Unidad aritmética con detector de desbordamiento .................................... 206

10.4 Componentes ...................................................................................................... 208

10.5 Verificación experimental .................................................................................... 208

10.5.1 Módulo sumador ......................................................................................... 208

10.5.2 Módulo sumador/restador ........................................................................... 208

10.5.3 Unidad aritmética con detector de desbordamiento .................................... 209

10.6 Ejercicios y cuestiones de refuerzo ..................................................................... 209

PARTE 3 Lógica secuencial síncrona ................................................. 211

11 Generación de señal de reloj con circuitos astables .............................. 215

11.1 Introducción ......................................................................................................... 215

11.2 Diseño de un multivibrador astable con puertas lógicas ..................................... 216

11.3 Diseño de un multivibrador astable con el 555 .................................................... 218

11.4 Simulación ........................................................................................................... 221

11.5 Componentes ...................................................................................................... 222

11.6 Verificación experimental .................................................................................... 223

11.7 Ejercicios y cuestiones de refuerzo ..................................................................... 224

12 Contador de rizo módulo 8 con biestables T ............................................ 225

12.1 Introducción ......................................................................................................... 225

12.2 Dos implementaciones de un contador de rizo ................................................... 228

12.2.1 Contador módulo 8 diseñado con biestables J ? K .................................... 228

12.2.2 Contador módulo 8 diseñado con biestables D .......................................... 229

12.3 La problemática de los estados espurios ............................................................ 229

12.4 Simulación ........................................................................................................... 231

12.4.1 Respuesta del contador diseñado con biestables J ? K ............................ 231

12.4.1.1 Filtrado de los estados espurios mediante registro ............................ 233

12.4.2 Respuesta del contador diseñado con biestables D ................................... 235

Componentes ...................................................................................................... 238

12.6 Verificación experimental ..................................................................................... 238

12.7 Ejercicios y cuestiones de refuerzo ..................................................................... 239

13 Contador de rizo módulo 8 con el 74x90 .................................................... 241

13.1 Introducción ......................................................................................................... 241

13.2 Diseño de un contador módulo 8 con el 74x90 .................................................... 247

13.3 La problemática de los estados espurios ............................................................. 250

13.4 Simulación ........................................................................................................... 251

13.4.1 Secuencia de estados del contador módulo 8 ............................................. 251

13.4.2 Filtrado de los estados espurios mediante registro .................................... 253

13.4.3 Decodificación de estados con el 7448 ...................................................... 254

13.5 Componentes ...................................................................................................... 255

13.6 Verificación experimental ..................................................................................... 256

13.7 Ejercicios y cuestiones de refuerzo ..................................................................... 256

14 Contador síncrono reversible módulo 4 con biestables J ? K ............... 257

14.1 Introducción ......................................................................................................... 257

14.2 Diseño de un contador síncrono reversible módulo 4 ......................................... 261

14.3 Simulación ........................................................................................................... 265

14.3.1 Implementación del diseño con el CI 7473 .................................................. 265

14.3.1.1 Entrada de control S constante .......................................................... 266

14.3.1.2 Cambio de nivel lógico de S con señal de reloj en estado bajo .......... 267

14.3.1.3 Cambio de nivel lógico de S con señal de reloj en estado alto ........... 269

14.3.1.4 Conclusiones ...................................................................................... 272

14.3.2 Implementación del diseño con el CI 74LS73A ........................................... 273

14.4 Componentes ...................................................................................................... 274

14.5 Verificación experimental ..................................................................................... 275

14.6 Ejercicios y cuestiones de refuerzo ..................................................................... 276

15 Contadores síncronos con el 74x163 ......................................................... 277

15.1 Introducción ......................................................................................................... 277

15.2 Diseño de contadores con el 74x163 ................................................................... 280

15.2.1 Contador en modo de carrera libre (módulo 16) ......................................... 280

15.2.2 Contador módulo 13 con la secuencia 0,1,?,12 ......................................... 281

15.2.3 Contador módulo 12 con la secuencia 3,4,?,14 ......................................... 281

15.2.4 Contador módulo 146 con la secuencia 0,1,?,145 ..................................... 282

15.3 Simulación ........................................................................................................... 283

15.3.1 Contador en modo de carrera libre (módulo 16) ......................................... 283

15.3.2 Contador módulo 13 con la secuencia 0,1,?,12 ......................................... 284

15.3.3 Contador módulo 12 con la secuencia 3,4,?,14 ......................................... 285

15.3.4 Contador módulo 146 con la secuencia 0,1,?,145 ..................................... 286

15.4 Componentes ...................................................................................................... 288

15.5 Verificación experimental ..................................................................................... 289

15.6 Ejercicios y cuestiones de refuerzo ..................................................................... 289

16 Segundero digital con contadores modulares .......................................... 291

16.1 Introducción ......................................................................................................... 291

16.2 Tres diseños de un segundero con contadores síncronos .................................. 292

16.2.1 Combinación de dos 74x163 ..................................................................... 292

16.2.2 Combinación de un 74x162 y un 74x163 ................................................... 293

16.2.3 Combinación de un 74x162 y un 74x161 ................................................... 294

16.3 Simulación ........................................................................................................... 295

16.4 Componentes ...................................................................................................... 300

16.5 Verificación experimental .................................................................................... 300

16.5.1 Contador módulo 10 (unidades del segundero) ......................................... 301

16.5.2 Contador módulo 6 (decenas del segundero) ............................................ 301

16.5.3 Segundero digital completo ....................................................................... 301

16.6 Ejercicios y cuestiones de refuerzo ..................................................................... 303

17 Decodificación de los estados de un contador ........................................ 305

17.1 Introducción ......................................................................................................... 305

17.2 Decodificación de contadores modulares ............................................................ 306

17.2.1 Decodificación de un contador asíncrono .................................................. 306

17.2.2 Decodificación de un contador síncrono .................................................... 307

17.3 Riesgo de interferencias en las líneas decodificadas .......................................... 308

17.3.1 Eliminación del riesgo de interferencias en la decodificación .................... 309

17.3.1.1 Habilitación desfasada del decodificador ........................................... 309

17.3.1.2 Filtrado mediante registro .................................................................. 310

17.3.1.3 Decodificación directa con un contador en anillo ............................... 311

17.4 Simulación ........................................................................................................... 311

17.4.1 Decodificación de contadores 74x90 con dispositivos 74x138 ................. 312

17.4.2 Decodificación de contadores 74x163 con dispositivos 74x42 ................. 316

17.4.3 Eliminación del riesgo de interferencias en la decodificación .................... 319

17.4.3.1 Habilitación desfasada del decodificador ........................................... 319

17.4.3.2 Filtrado mediante registro .................................................................. 320

17.5 Componentes ...................................................................................................... 321

17.6 Verificación experimental .................................................................................... 322

17.7 Ejercicios y cuestiones de refuerzo ..................................................................... 322

18 Registro de desplazamiento de 4 bits con biestables D .......................... 325

18.1 Introducción ......................................................................................................... 325

18.2 Diseño de un registro de desplazamiento de 4 bits ............................................. 326

18.3 Simulación ........................................................................................................... 327

18.3.1 Entrada serie y salida en paralelo ............................................................... 327

18.3.2 Entrada en paralelo y salida en paralelo ..................................................... 328

18.4 Componentes ...................................................................................................... 329

18.5 Verificación experimental .................................................................................... 330

18.6 Ejercicios y cuestiones de refuerzo .............................................

Si quiere tener a su alcance una colección de casos de estudio sobre diseño lógico digital, expuestos en capítulos individuales a modo de sesiones prácticas, ha llegado al libro indicado. En él se recurre a una versión gratuita del versátil programa PSpice para simular un amplio abanico de diseños digitales como paso previo a la verificación experimental de su funcionamiento, que se realizará mediante el cableado manual sobre placas de prototipos de circuitos integrados digitales de pequeña y mediana escala de integración. Gracias a los dispositivos lógicos de función fija y bajo coste, que integran desde simples puertas lógicas y biestables hasta decodificadores, multiplexores, sumadores, contadores y registros de desplazamiento, es posible experimentar con todos los diseños propuestos en el libro sin necesidad de contar con sofisticados recursos. El presente texto constituye, por tanto, un complemento formativo orientado a afianzar el aprendizaje de los fundamentos de la disciplina mediante un enfoque práctico que, además, le facilitará el abordaje del diseño de sistemas digitales mediante lenguajes de descripción hardware en una etapa adicional del aprendizaje. En esta tercera edición el material se ha agrupado en cinco partes. La primera de ellas persigue una primera toma de contacto con los circuitos integrados digitales a partir de sencillos montajes orientados a la caracterización eléctrica y temporal de puertas lógicas. La segunda parte incide en cuestiones de lógica puramente combinacional mediante diseños implementados tanto con puertas lógicas como con dispositivos modulares. En la tercera y cuarta parte se aborda el estudio de la lógica secuencial síncrona y asíncrona, respectivamente. La quinta y última parte comprende una variada selección de aplicaciones de las funciones lógicas de uso común que complementan el material previo y abren la puerta al estudio de una serie de áreas temáticas enraizadas en los fundamentos de las tecnologías electrónicas digitales, entre las que destacan los computadores y su estructura, los sistemas electrónicos de comunicaciones, el desarrollo de sistemas empotrados basados en microcontrolador y la implementación de diseños digitales empleando lógica configurable. Sin duda, este libro le será de gran utilidad si desea profundizar en la electrónica digital o si es un estudiante universitario que cursa asignaturas sobre dicha materia. Javier Vázquez del Real es profesor titular del área de Tecnología Electrónica de la Universidad de Castilla-La Mancha.